Cacbua silic (SiC) là một vật liệu quan trọng trong ngành công nghiệp bán dẫn, vì nó được sử dụng cho các đặc tính kỹ thuật và vật lý của nó trong các mạch hiện đại. Các thiết bị SiC đang cách mạng hóa điện tử công suất trong các ngành công nghiệp, mang lại hiệu quả, mật độ năng lượng và độ tin cậy cao hơn trong các ứng dụng như xe điện, hệ thống năng lượng tái tạo và ổ đĩa công nghiệp.

Ở đây chúng tôi nhấn mạnh cách EEMCO, một nhà sản xuất vật liệu SiC, hợp lý hóa quy trình phân tích hình ảnh của mình cho các tấm SiC khắc hoàn chỉnh thông qua sự hợp tác với Evident. Kết quả của công việc này, phần mềm tùy chỉnh của chúng tôi với khả năng học máy đã cải thiện độ chính xác và hiệu quả của việc phát hiện và mô tả khuyết tật trên các tấm wafer. Tìm hiểu thêm về sự đổi mới này và tác động của nó trong các ngành.

Ứng dụng thiết bị SiC

Ba ứng dụng chính của thiết bị SiC là trong ngành công nghiệp ô tô, điện tử công suất cao và năng lượng tái tạo.

1. Ô tô

Nhu cầu về truyền động điện trong xe ô tô đang tăng lên nhanh chóng. Với thị phần hơn 60%, ổ điện là một yếu tố quan trọng trên thị trường thiết bị điện tử công suất cao. 1 Điều này đã tạo ra nhu cầu ngày càng tăng về chất bán dẫn công suất hiệu quả cao để sử dụng trong xe điện / hybrid (EV / HEV).

Ứng dụng này ngay lập tức gợi ý việc sử dụng chất bán dẫn công suất dựa trên SiC, vì chúng có lợi thế rõ ràng so với các thành phần dựa trên Si thông thường. Hiệu suất và mật độ năng lượng cao hơn do SiC cung cấp dẫn đến tăng phạm vi, kích thước hệ thống nhỏ hơn và thời gian sạc nhanh hơn. Các ứng dụng điển hình bao gồm bộ biến tần hiệu quả cao, thiết bị điện tử sạc trên bo mạch, bộ tăng áp và bộ chuyển đổi DC / DC.

Một trong những tiêu chí thiết yếu cho việc sử dụng tiết kiệm các tinh thể đơn SiC là mật độ khuyết tật thấp nhất có thể trong một tinh thể đơn kết hợp với tấm tinh thể lớn nhất có thể (wafer 6 inch hiện là tiêu chuẩn, với các tấm wafer 8 inch sẽ sớm được giới thiệu). Điều này đòi hỏi phải làm chủ công nghệ trồng tinh thể phức tạp, chẳng hạn như công nghệ do EEMCO cung cấp.

2. Điện tử công suất cao

Một loạt các ứng dụng công nghiệp được thúc đẩy bởi nhu cầu cung cấp năng lượng phụ trợ. Các ứng dụng này thường bao gồm ổ đĩa cơ, biến tần và thiết bị sản xuất công nghiệp (bao gồm cả robot).

Với các đặc tính độc đáo của nó, cacbua silic hỗ trợ mạnh mẽ việc cải thiện hiệu quả năng lượng, độ tin cậy và hiệu suất của các hệ thống này.5 Các thiết bị điển hình sử dụng công nghệ dựa trên SiC bao gồm từ điốt Schottky (còn được gọi là điốt rào cản Schottky, hoặc SBD) đến bóng bán dẫn hiệu ứng trường cổng nối (JFET) và bóng bán dẫn hiệu ứng trường bán dẫn oxit kim loại (MOSFET).

Trên thực tế, SiC SBD được sử dụng rộng rãi trong các mô-đun nguồn bóng bán dẫn lưỡng cực cổng cách điện (IGBT) và mạch hiệu chỉnh hệ số công suất (PFC). SiC không chỉ tăng hiệu quả và giảm yêu cầu làm mát trong các ứng dụng này. Nó cũng đơn giản hóa thiết kế thiết bị, trong đó nó làm giảm số lượng các thành phần thụ động và cho phép thiết kế đơn giản hơn mà không làm giảm hiệu suất. Những đặc điểm này cũng hữu ích trong ngành CNTT, đặc biệt là trong các trung tâm dữ liệu.

3. Năng lượng tái tạo

Năng lượng mặt trời, năng lượng gió và lưu trữ năng lượng tái tạo là những ngành công nghiệp cho thấy sự tăng trưởng đáng kể. Ngành năng lượng tái tạo là một lĩnh vực cân bằng cung và cầu một cách hiệu quả và hiệu quả. Trong khi năng lượng tái tạo đã là một ứng dụng ưa thích cho các sản phẩm SiC trong nhiều năm, các cuộc khủng hoảng khí hậu và năng lượng hiện nay đã làm tăng nhu cầu về các nguồn năng lượng thay thế hơn nữa.

Các ứng dụng phổ biến liên quan đến các thiết bị năng lượng điện tử hiệu quả cao như biến tần và bộ tăng áp (bộ chuyển đổi điện), cũng như các thành phần thiết yếu để chuyển đổi năng lượng và hệ thống lưu trữ năng lượng. Tổn thất sạc điển hình cho các thiết bị như vậy nằm trong khoảng từ 6 đến 9%, con số có thể giảm đáng kể bằng cách áp dụng công nghệ SiC. 1 Công nghệ thiết bị dựa trên SiC cũng làm giảm nhu cầu thiết kế mạch phức tạp, đòi hỏi ít thành phần tổng thể hơn.

Kiểm soát và giám sát chất lượng sản phẩm cuối cùng của SiC Wafer

Với nhu cầu về công nghệ thiết bị dựa trên SiC trong nhiều ngành công nghiệp, các nhà sản xuất SiC đang tập trung vào sự đổi mới, chất lượng và hiệu quả trong quy trình sản xuất của họ. Một ví dụ là EBNER EUROPEAN MONO CRYSTAL OPERATION (EEMCO), một công ty khởi nghiệp tách ra từ EBNER vào năm 2020.

“EEMCO là công ty độc lập đầu tiên ở châu Âu nhằm sản xuất hàng loạt chất nền SiC 200 mm cho ngành công nghiệp bán dẫn”, Mirko Löhmann, chịu trách nhiệm về kỹ thuật quy trình tại EEMCO giải thích.

Tận dụng 12 năm kinh nghiệm R &D trong thiết kế và sản xuất thiết bị tăng trưởng tinh thể, công ty Áo phát triển lò chuyên dụng cho quá trình tăng trưởng tinh thể đơn 4H SiC và đang thực hiện bước tiếp theo với boules và pucks 200 mm.

Tại cơ sở Leonding, Áo, đội ngũ chuyên gia quốc tế của EEMCO nuôi cấy các tinh thể đơn SiC cho ngành công nghiệp bán dẫn.

“Những tinh thể này được sử dụng trong các ứng dụng năng lượng cao, đặc biệt là trong lĩnh vực ô tô, công nghiệp và năng lượng tái tạo”, Sebastian Hofer, người giám sát kỹ thuật khuyết tật tại EEMCO cho biết.

EEMCO vận hành ngày càng nhiều lò nung trong đó các tinh thể đơn SiC phát triển bằng quy trình vận chuyển hơi vật lý (PVT), tạo thành một tinh thể duy nhất trong pha hơi SiC.

“Mục tiêu của chúng tôi là sản xuất các sản phẩm chiến lược, công nghệ cao với tư cách là công ty châu Âu độc lập đầu tiên sản xuất các loại tinh thể SiC này, cung cấp một giải pháp thay thế chất lượng cao cho sự phụ thuộc vào các nhà cung cấp ở Mỹ hoặc Trung Quốc”, Hofer nói. Löhmann cho biết thêm, “Là một sản phẩm bền vững và tiết kiệm năng lượng, SiC cũng góp phần đáng kể vào việc giảm CO2 trên các thị trường khác nhau và các sản phẩm tiêu dùng cuối cùng.”

Chuyên về pucks 150 và 200 mm chất lượng cao, EEMCO tận dụng lò độc quyền và công nghệ xử lý. “Trong hai năm qua, chúng tôi đã nộp hơn 30 bằng sáng chế liên quan đến thiết bị và quy trình tăng trưởng tinh thể SiC. Chiến lược của chúng tôi là phát triển các tinh thể đơn SiC 150 và 200 mm để sản xuất và cung cấp phôi toàn cầu, tập trung chủ yếu vào khách hàng châu Âu”, Hofer giải thích.

Để kiểm soát và giám sát quá trình sản xuất và chất lượng sản phẩm cuối cùng, cần phải phân tích quang học 100% toàn bộ tấm SiC đường kính 150 hoặc 200 mm. Điều này đặt ra hai thách thức:

- Hình ảnh độ phân giải cao: Để có được hình ảnh có độ phân giải cao (1-2 μm / pixel) của toàn bộ tấm wafer cần có thời gian và tạo ra hàng gigabyte dữ liệu trên mỗi tấm wafer.

- Phát hiện trật khớp: Phân tích hạt truyền thống là không đủ để phát hiện các trật khớp phân cụm và chồng chéo. Phân đoạn dựa trên ngưỡng đơn giản thiếu độ chính xác cho các kết quả có ý nghĩa.

“Chúng tôi cần thu thập và phân tích các tấm SiC khắc hoàn chỉnh”, Löhmann nói. “Chúng tôi đã hợp tác với nhóm Giải pháp tùy chỉnh tại Trung tâm Công nghệ Evident Châu Âu (ETCE) để phát triển một giải pháp dựa trên phần mềm PRECiV™, nền tảng hình ảnh công nghiệp Evident mà chúng tôi sử dụng trong phòng thí nghiệm của mình”, ông tiếp tục. Sự hợp tác này sử dụng học máy để cải thiện đặc tính khuyết tật trên các tấm SiC được khắc hoàn chỉnh.

Thiết kế một giải pháp tùy chỉnh để phân tích quang học của các tấm SiC lớn

Tiến sĩ Norbert Radomski và Tiến sĩ Sergej Bock, các nhà quản lý giải pháp trong Nhóm Giải pháp Tùy chỉnh (CSG) của Trung tâm Công nghệ Evident Châu Âu (ETCE), giải thích những ưu điểm của giải pháp kiểm tra wafer tùy chỉnh này.

“Với việc mua lại và phân tích các tấm wafer SiC khắc hoàn chỉnh, chúng tôi đã tăng danh mục các giải pháp kiểm tra wafer. 2, 3 Bây giờ chúng ta có thể thu thập và phân tích hoàn thành 6 inch. và 8 inch. tấm silicon cacbua khắc”, Norbert nói. Sergej cho biết thêm, “Giải pháp sử dụng học máy để cải thiện đặc tính lỗi. Ngoài ra, việc phân tích được thực hiện song song với việc thu thập dữ liệu để nâng cao hiệu quả”.

Giải pháp kiểm tra này rất quan trọng để xác định và mô tả các khuyết tật có thể xảy ra trong quá trình tăng trưởng tinh thể SiC.

Tinh thể SiC được phát triển bằng phương pháp vận chuyển hơi vật lý (PVT), trong đó một tinh thể duy nhất được phát triển trong pha hơi SiC. Kiểm soát ứng suất tinh thể trong quá trình tăng trưởng là chìa khóa để giảm thiểu mật độ khuyết tật mở rộng, chẳng hạn như micropipes (MP), trật khớp mặt phẳng cơ bản (BPD), trật khớp vít ren (TSD) và trật khớp cạnh ren (TED). 4 Những khiếm khuyết này ảnh hưởng đến tính chất điện của tấm SiC. Phương pháp khắc KOH nóng chảy được coi là một phương pháp hiệu quả để mô tả trật khớp trong SiC. 5

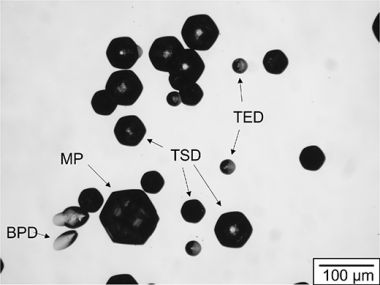

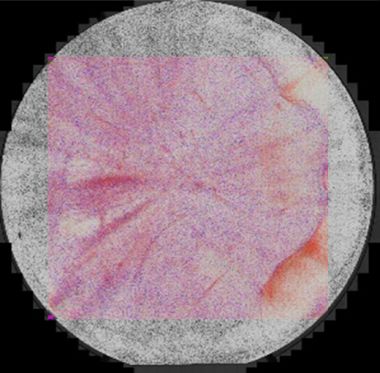

Ví dụ, Hình 1 cho thấy các loại khuyết tật khác nhau trên tấm SiC được khắc, chẳng hạn như trật khớp mặt phẳng cơ bản micropipes (MP), trật khớp vít ren (TSD) và trật khớp cạnh ren (TED).

Hình 1. Hình ảnh kính hiển vi của các khuyết tật điển hình trên tấm SiC được khắc KOH.6 Nguồn ảnh: MDPI.

Yêu cầu từ EEMCO đưa ra cho Evident: Để kiểm soát và giám sát quá trình sản xuất và chất lượng của sản phẩm cuối cùng, một phân tích quang học 100% của 6 in. hoặc 8 in. đường kính SiC wafer phải được thực hiện.

Đây là một thách thức khá lớn, Norbert nói: “Đầu tiên, người ta cần hình ảnh có độ phân giải cao (1-2 μm / pixel) của toàn bộ tấm wafer, chiếm thời gian và tạo ra hàng gigabyte (GB) dữ liệu trên mỗi tấm wafer. Thứ hai, việc phát hiện trật khớp không thể được thực hiện với phân tích hạt cổ điển. Các trật khớp có xu hướng phân cụm và chồng chéo, vì vậy phân đoạn dựa trên ngưỡng đơn giản không đủ chính xác để cung cấp kết quả có ý nghĩa.

Ngưỡng không phát hiện các cấu trúc cụ thể trong hình ảnh. Thay vào đó, nó phát hiện nhiều đối tượng cùng một lúc mà không phân biệt giữa chúng7, dựa trên các giá trị cường độ xám hoặc RGB được xác định trước. Sergej lưu ý, “Ngược lại, học máy hình thành các quy tắc để phát hiện đối tượng dựa trên nhiều ví dụ về đại diện của các đối tượng quan tâm.” Đánh giá tự động, dựa trên các mạng thần kinh nhân tạo sâu đã học cách phân loại các khu vực hình ảnh độc lập với Trước đây đã đặt các giá trị ngưỡng trong hình ảnh, giúp việc phân tích hình ảnh trở nên dễ dàng và chính xác hơn. 7

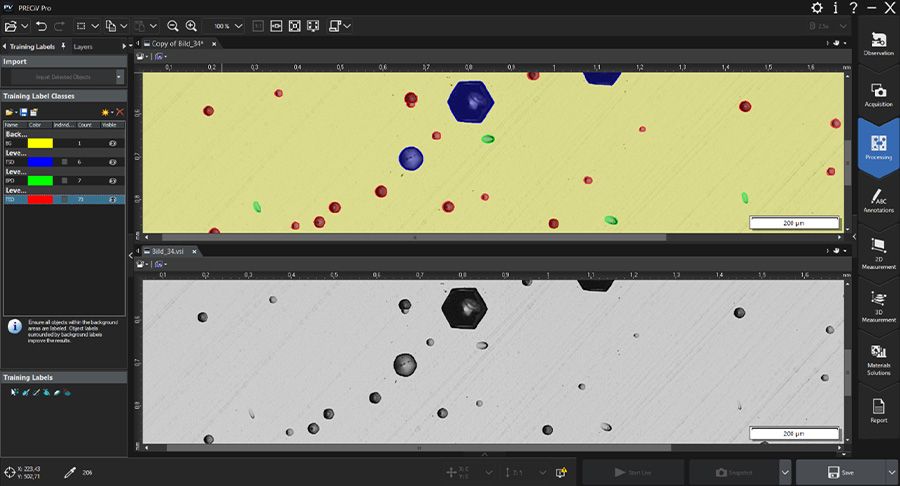

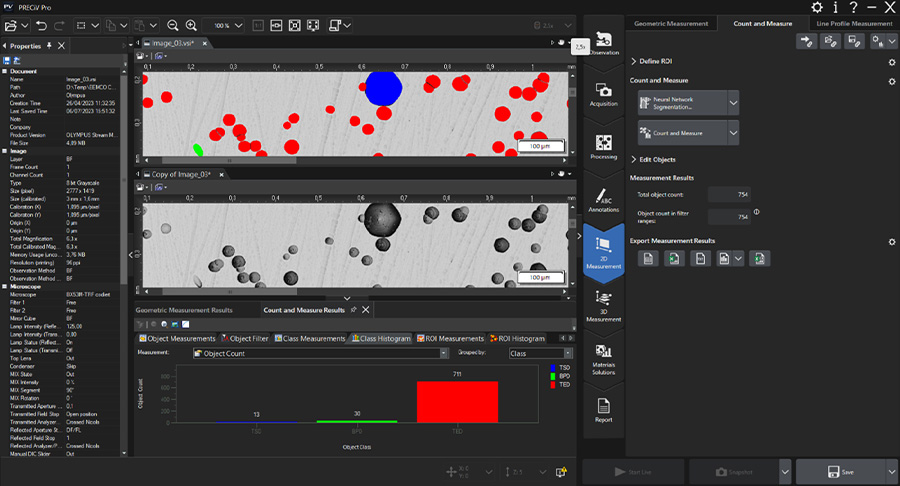

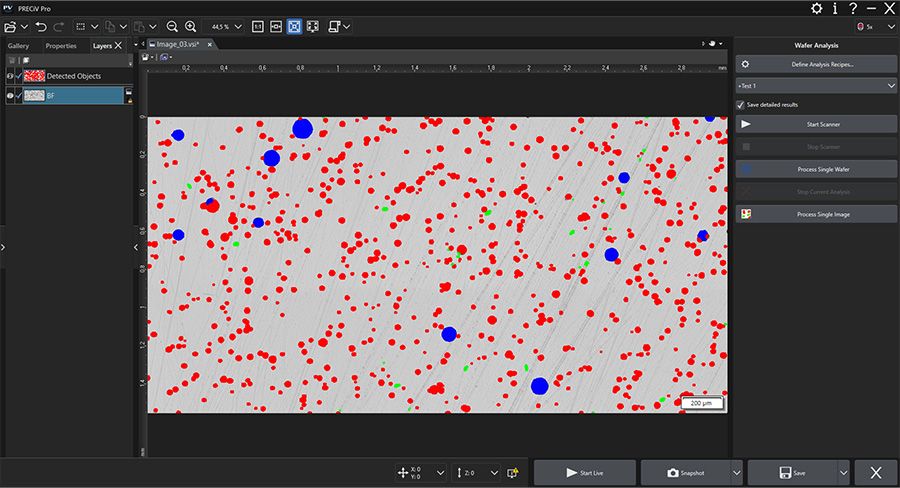

Nhóm Giải pháp tùy chỉnh đã chứng minh rằng một phương pháp phân đoạn sử dụng mạng thần kinh được đào tạo thích hợp (xem Hình 2) có thể được sử dụng để tự động tách các trật khớp phân cụm và chồng lên nhau (xem Hình 3), dẫn đến phân tích mật độ khuyết tật đầy đủ.

Hình 2. Ảnh chụp màn hình nhãn đào tạo trật khớp (phần trên) và hình ảnh trường sáng của tấm SiC được khắc (độ phân giải hình ảnh: 1,095 μm / pixel).

Hình 3. Ảnh chụp màn hình các trật khớp được phát hiện do phân đoạn mạng thần kinh (phần trên) và hình ảnh trường sáng của tấm SiC khắc (độ phân giải hình ảnh: 1,095 μm / pixel). Lưu ý rằng trật khớp cụm và lớp phủ được tách ra.

Tuy nhiên, cần lưu ý rằng cả việc đào tạo mạng thần kinh và thực thi mạng thần kinh đều đòi hỏi rất nhiều sức mạnh tính toán, thường được cung cấp bởi hàng trăm hoặc hàng nghìn lõi Kiến trúc thiết bị hợp nhất tính toán (CUDA) của card đồ họa NVIDIA hỗ trợ CUDA.

“Một hình ảnh tổng thể của một tấm 6 in. Tấm wafer được chụp ảnh với độ phân giải 1,095 μm / pixel bao gồm khoảng 4.000 hình ảnh đơn lẻ và có kích thước khoảng 25 GB. Tính toán một phân đoạn bởi một mạng lưới thần kinh trên toàn bộ hình ảnh sẽ mất hàng giờ ngay cả với một card đồ họa hiện đại, “Sergej giải thích.

Do đó, vì tiêu chí chất lượng của tấm SiC là mật độ trật khớp trên mỗi khu vực, cách tiếp cận của giải pháp tùy chỉnh là chia quy trình thành phương pháp mua lại và phương pháp phân tích sử dụng hai PC để làm việc song song. Điều này tăng gấp đôi thông lượng, nâng cao hiệu quả.

Norbert giải thích giải pháp tùy chỉnh tổng thể: “Hình ảnh của toàn bộ tấm wafer được chụp bởi hệ thống thu nhận được lưu trữ ở một vị trí được xác định trước. Tệp trạng thái cho biết liệu hình ảnh đã hoàn chỉnh và có thể được phân tích bằng giải pháp phân tích tấm wafer khuyết tật dựa trên mạng nơ-ron hay không. Với giải pháp phân tích wafer, hình ảnh wafer lớn được chia thành các hình ảnh gạch nhỏ hơn với kích thước có thể xác định và quy trình phân tích hàng loạt với phân đoạn mạng nơ-ron được áp dụng cho mỗi ô. Các Tính toán trên các gạch nhỏ hơn cải thiện hiệu quả. Kết quả cũng cung cấp số mật độ trật khớp trên mỗi khu vực gạch riêng lẻ. Vì vị trí của gạch trên tấm wafer đã được biết đến, đầu ra về cơ bản là bản đồ mật độ của toàn bộ tấm wafer.

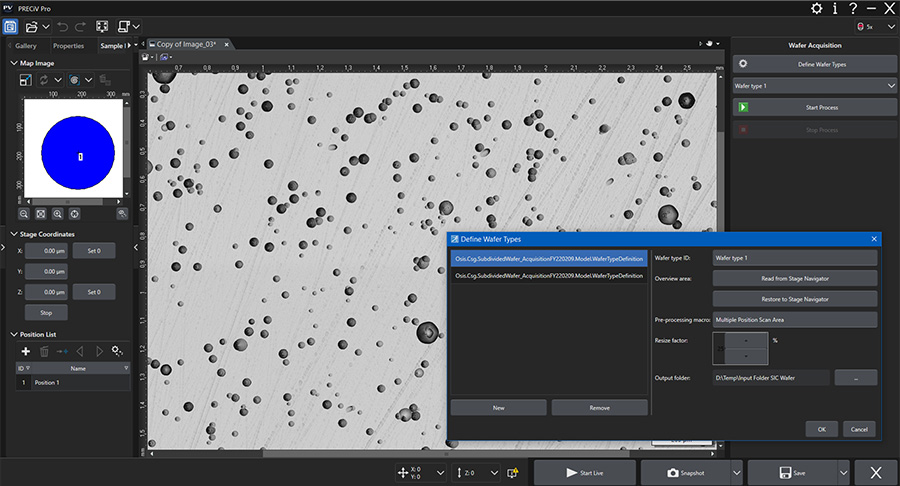

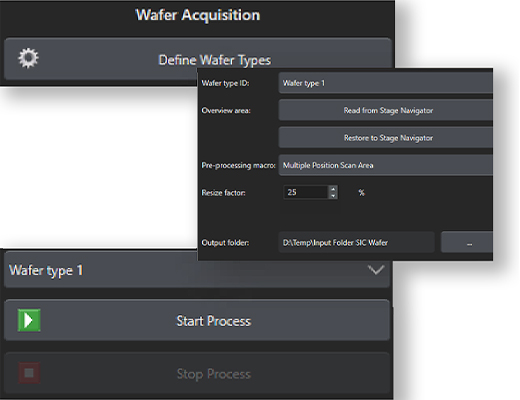

Bây giờ chúng ta hãy xem xét quy trình làm việc của giải pháp tùy chỉnh, bắt đầu bằng việc chụp lại wafer (xem Hình 4).

Hình 4. Ảnh chụp màn hình của giải pháp thu nhận wafer hiển thị hộp thoại định nghĩa quy trình cho Xác định loại wafer.

Dưới đây là các bước để có được hình ảnh toàn cảnh lớn của toàn bộ tấm SiC (xem Hình 5). Tệp hình ảnh kết quả (định dạng VSI độc quyền của chúng tôi) sau đó được sử dụng trong quy trình phân tích.

Quy trình mua lại SiC Wafer

Hình 5. Quy trình chụp ảnh tùy chỉnh để kiểm tra tấm SiC. Hình 5. Quy trình chụp ảnh tùy chỉnh để kiểm tra tấm SiC. |

Xác định các loại wafer:

Danh sách thả xuống: Chọn công thức chụp ảnh được xác định trước từ ID loại wafer.Bắt đầu quá trình: Bắt đầu quá trình mua lại được xác định trước. Hộp thoại đầu vào sẽ mở ra để đặt ID sản phẩm và số đo (sẽ được tăng tự động). Sau đó, phần mềm sẽ tự động tính toán hiệu chỉnh Z mặt phẳng nghiêng dựa trên giá trị Z của ba vị trí bàn. Các giá trị Z được xác định bởi tự động lấy nét.Dừng máy quét: Dừng quá trình mua lại. |

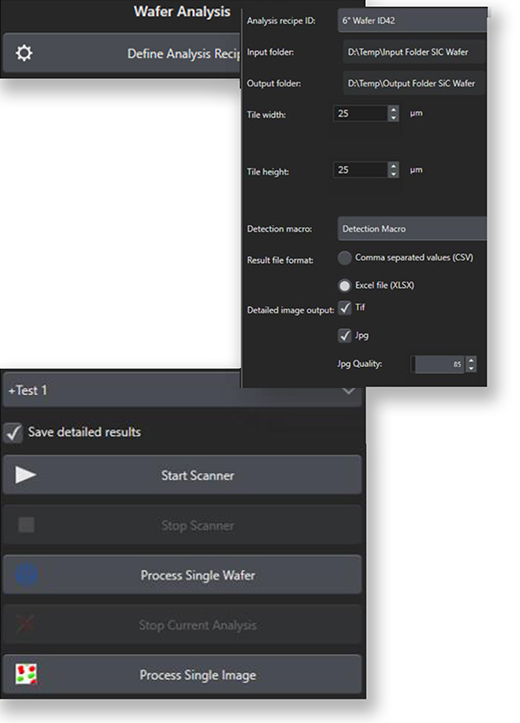

Với giải pháp phân tích wafer, hình ảnh wafer lớn được chia thành các hình ảnh ô nhỏ hơn và một macro được xác định trước (ở đây, giải pháp Đếm và Đo lường với phân đoạn mạng nơ-ron) được áp dụng trong một quy trình hàng loạt trên mỗi ô (xem Hình 6).

Hình 6. Ảnh chụp màn hình của giải pháp phân tích wafer hiển thị hộp thoại định nghĩa quy trình cho Xác định công thức phân tích.

Quy trình phân tích SiC Wafer

Hình 7. Quy trình phân tích tùy chỉnh để kiểm tra tấm SiC. Hình 7. Quy trình phân tích tùy chỉnh để kiểm tra tấm SiC. |

Xác định công thức phân tích:

Drop Down List: Chọn công thức phân tích được xác định trước.Start Scanner: Kiểm tra thư mục đầu vào cho các tệp VSI với tệp trạng thái liên quan cho biết trạng thái hình ảnh là có được (sẵn sàng để xử lý). Bắt đầu quá trình hàng loạt (cắt hình ảnh thành các ô phụ và thực hiện phân tích).Stop Scanner:Dừng chức năng máy quét.Process Single Wafer: Chọn một hình ảnh VSI duy nhất để xử lý.Stop Current Analysis: Dừng phân tích đang chạy.Process Single Image:Chọn một hình ảnh TIF duy nhất để xử lý. |

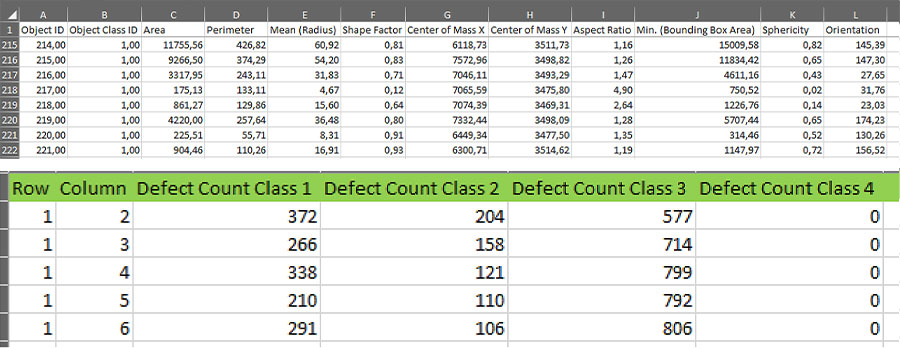

Kết quả kiểm tra SiC Wafer

Kết quả có thể được xuất dưới dạng tệp CSV hoặc XLSX để cung cấp dữ liệu cho mỗi ô với thông tin riêng lẻ về các lỗi được phát hiện (Hình 8, hình ảnh trên cùng) hoặc dưới dạng bảng tóm tắt với các lớp lỗi trên mỗi ô (Hình 8, hình dưới cùng). Trang tính đầu tiên này bao gồm một hình ảnh trên mỗi ô, cùng với ID đối tượng (khuyết tật đã xác định) và tâm khối lượng của chúng theo hướng X, tâm khối lượng theo hướng Y và các giá trị mô tả khác nhau cho hình dạng của chúng, chẳng hạn như hình cầu và hướng.

Tệp tóm tắt hiển thị ID hàng và cột của tất cả các ô con và số lỗi riêng lẻ cho mỗi lớp. Mỗi lớp đại diện cho một loại lỗi cụ thể (xem Hình 1 để biết ví dụ). Cuối cùng, phần mềm cung cấp hình ảnh tổng quan về tấm SiC (Hình 9) dưới dạng TIF với lớp phát hiện hiển thị mã màu cho lớp trên mỗi khuyết tật. Đối với mục đích tài liệu, hình ảnh JPEG nén với lớp phủ phát hiện burned-in cũng là một tùy chọn. Cùng với nhau, những hình ảnh và dữ liệu có tổ chức này cho phép phân tích hiệu quả các khuyết tật trên toàn bộ tấm wafer.

Hình 8. Kết quả kiểm tra tấm SiC được xuất dưới dạng tệp CSV hoặc XLSX cung cấp chi tiết về các khuyết tật, bao gồm số lượng của chúng trên mỗi lớp, hình dạng của chúng và các thông số khác.

Hình 9. Hình ảnh tổng quan của toàn bộ tấm SiC.

Tổng kết

Sự hợp tác giữa EEMCO và Evident trong việc hợp lý hóa các quy trình thu thập và phân tích hình ảnh cho các tấm SiC khắc nhấn mạnh cam kết của chúng tôi đối với sự đổi mới và chất lượng trong sản xuất SiC. Thông qua phần mềm tùy chỉnh và học máy, đặc tính khuyết tật trên tấm SiC đã được cải thiện đáng kể, mở đường cho chất lượng và hiệu suất sản phẩm được nâng cao trên các ứng dụng đa dạng. Khi nhu cầu về các thiết bị dựa trên SiC tiếp tục phát triển, những nỗ lực hợp tác như vậy minh họa cho Sự cống hiến của ngành công nghiệp để đáp ứng những thách thức công nghệ đang phát triển và thúc đẩy kỷ nguyên của thiết bị điện tử bền vững, hiệu suất cao